|

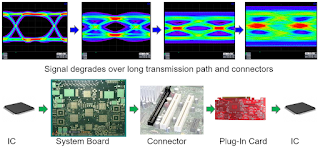

| Figure 1: These images depict the degradation of serial data traffic as it makes its way from transmitter to receiver |

In recent years, the data rates in serial links have increased exponentially across any number of standard protocols, including PCI Express, USB, and even SATA and SAS. With higher data rates comes more challenges for system designers, validation engineers, and test engineers with respect to signal integrity (SI). Some SI effects are much more prominent at higher data rates than they were for lower-speed versions of the same protocols. In this series of posts, we'll examine these SI effects, look at some methods of improving system performance, and discuss some SI analysis solutions as well as measurement considerations.

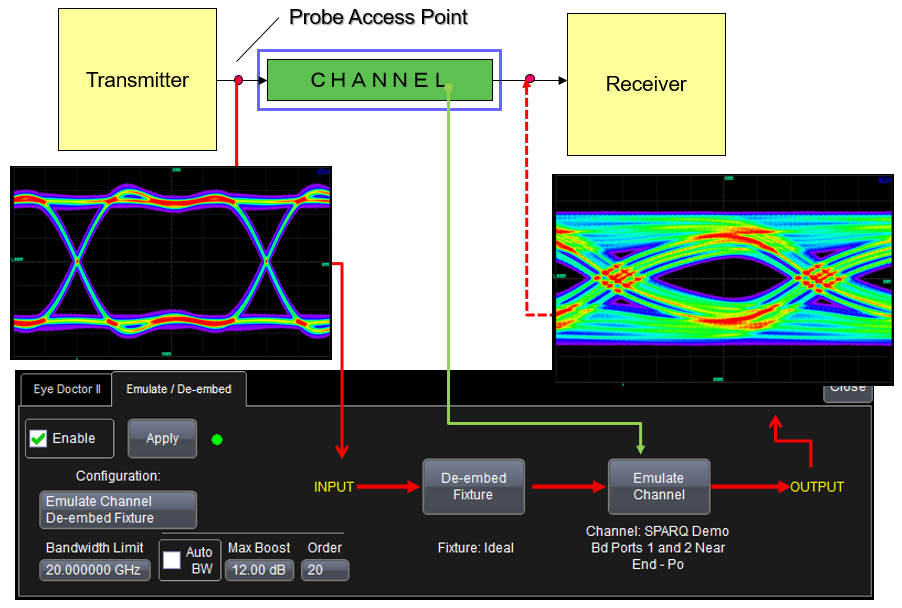

What does a typical high-speed serial channel look like? Referring to Figure 1, the signal typically enters the channel from a transmitter IC (at left). Right off the bat, there will be some amount of loss even within the IC package. The signal then traverses the system board, a backplane, and a board-to-board high-speed connector, perhaps a PCI Express CEM connector into which is plugged an add-in card (memory, graphics, or what have you). In each stage of this journey, the signal suffers further degradation.

By the time the signal reaches the receiver IC on the add-in card, where it takes a final hit from that IC's package, the signal has gone from the wide-open eye at top left in Figure 1 to the virtually closed eye at top right. At lower speeds, these effects are less prominent. But as data rates increase, it is imperative, even critical, to apply some techniques to improve signal performance at both ends of the channel. An important aspect of debugging high-speed serial links is to break up the signal into its constituent elements within the channel by visualizing and analyzing the signal at each point.

Prominent SI issues that can plague high-speed serial links are mainly of two types. Channel-related problems include:

Non-channel-related problems include excessive random or periodic jitter. Typically, periodic jitter might be caused by inefficient power supplies that leak lower-frequency periodic signals into the channel. Random jitter often stems from the clock/data recovery (CDR) circuitry, which also can introduce random noise.

Often, there's no single cause of havoc in a serial-data channel, but rather "death by a thousand cuts." It's common to find multiple effects happening at once and there's no single solution to remedy them all. They must be isolated and examined to find their root cause(s), which is why it's so important to be able to visualize the signal at all points in the link.

In subsequent posts, we'll begin looking at some of the channel-related issues in high-speed serial links.